A B C D E F G H I J K L M N O P Q R S T U V W X Y Z

A B C D E F G H I J K L M N O P Q R S T U V W X Y Z

كلية العلوم

القسم : الفيزياء

السنة : الثالثة

السؤال ورلاس محلولة

## الكرزونيات ٢

A 2 Z LIBRARY

مكتبة العلوم ( فيزياء ، كيمياء ، رياضيات ، علم الحياة )

يمكنكم طلب المحاضرات برسالة نصية (SMS) أو عبر (What's app) على الرقم TEL: 0931497960

A B C D E F G H I J K L M N O P Q R S T U V W X Y Z

### **السؤال الأول: أجب عن كل من الأسئلة الآتية**

**أولئك: أحب يصح أو خطأ مع تصحيح الإجابة الخاطئة:**

- 1- من أجل التحليل المستمر للترانزستور يكون ربع التيار الأمامي  $\beta$  هو النسبة بين تيار المجمع وتيار الباعث.

- 2- يعد الترانزستور MOSFET مضخماً للإشارة عندما يكون انحيازه في المنطقة الأمامية.

- 3- من أجل التحليل المستمر لدارة الترانزستور نستبدل المكفرات بدارة مقصورة.

- 4- أحد مميزات مكبر العمليات المماثلي أن مقاومة الخرج كبيرة جداً.

- 5- نسمى النسبة بين ربع الجهد في النمط التفاضلي وربع الجهد في النمط المشترك بنسبة رفض النمط المشترك

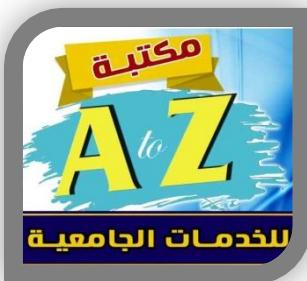

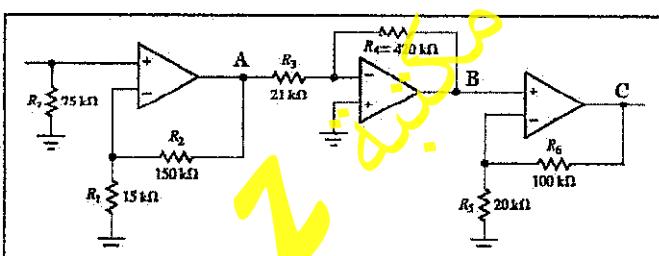

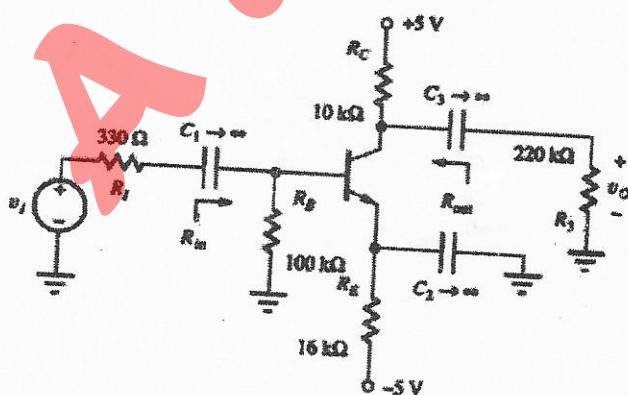

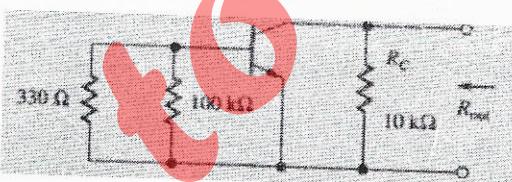

ثانياً: احسب قيمة ربع الجهد الكلي  $A_1$  للدارة المبينة في الشكل الآتي، ثم احسب جهود العقد A,B,C عند تطبيق إشارة دخل  $0.2V$ .

## السؤال الثاني: حل كل من المسائل الآتية

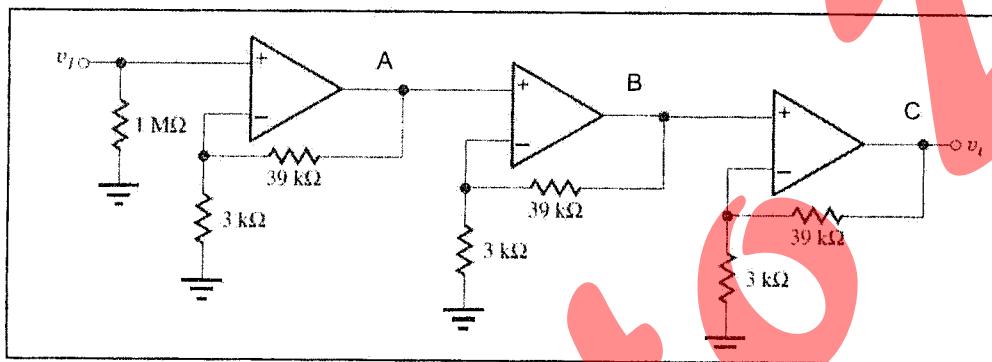

**أولاً:** لتكن لدينا الدارة المبينة في الشكل

$$\beta_F = 100, V_A = 75V, V_{CE} = 3.39V$$

$$= 0.025V$$

الدورة الخامسة لـ "الكتاب المقدس والحياة" ، إشراف دار الدعوة

من أجل تحقيق شرط الإشارة الصغيرة.

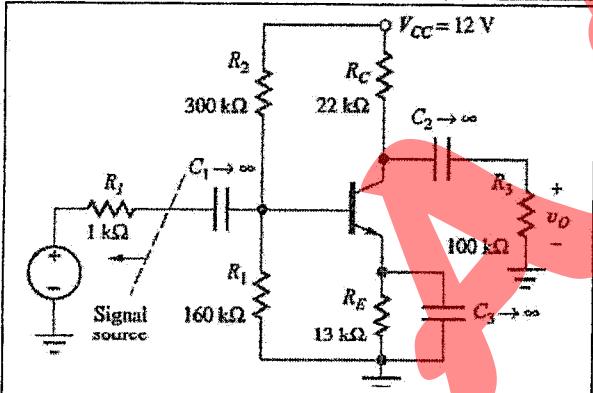

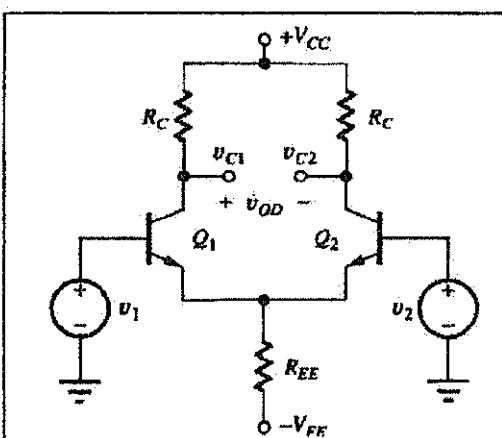

ثانياً: لتكن لدينا المضخم التفاضلي المبين بالشكل جانبأً والمطلوب:

١- أحسب احداثيات نقطة العمل للترانزستور في المضخم التالي

إذا علمت أنّ:

$$VCC = 12\text{ V}, VEE = 12\text{ V}, REE = 270\text{ k}\Omega,$$

$RC = 330 \text{ } k\Omega$ , and  $\beta F = 100$

2- في النمط التفاضلي أحسب الربح Add، وما هي مقاومة الدخل Rid، مقاومة الخرج Rod.

3- أحسب الربح في النمط المشترك CMMR، وأحسب نسبة رفض النمط المشترك في النمط المشترك.

الاسم:

الدرجة: 70

السؤال الأول: أجب بصح أو خطأ مع تصحيف الإجابة الخاطئة:

- 1- يُصمم مكير العمليات بحيث تكون المقاومة بين مدخليه مساوية الصفر.

- 2- يُعد الترانزستور BJT مخضماً ممتازاً لإشارات الدخل الجيبية عندما يكون انحيازه في منطقة الإشباع.

- 3- من أجل التحليل المتوازن لدارة الترانزستور نتبدل المقاومات بدارة مقسورة.

- 4- أحد مميزات مكير العمليات المثالي أن نسبة رفض النمط المشترك صغيرة جداً.

- 5- النمط المشترك هو الحالة الإيجابية لعمل المضخم التقاضي.

السؤال الثاني:

احسب قيمة ربع الجهد الكلي  $A_v$  للدارة المبينة في الشكل

جانباً.

السؤال الثالث:

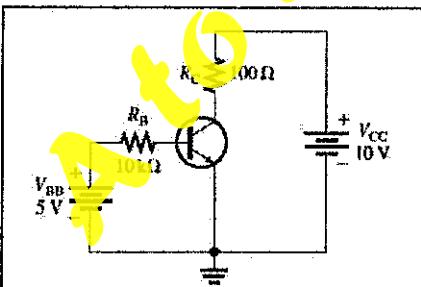

في الشكل المبين جانباً إذا علمت أن  $\beta = 150$ ,  $V_{BE} = 0.7V$  احسب  $I_B, I_C, I_E, V_{CE}$

السؤال الرابع:

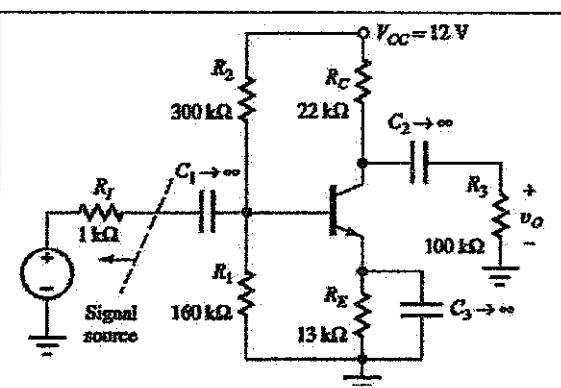

لتكن لدينا الدارة المبينة في الشكل الآتي، إذا علمت أن:  $\beta_F = 100, V_A = 75V, V_{CE} = 3.39V, I_C = 0.245mA, V_T = 0.025V$

احسب ربع الجهد الكلي للدارة والمطال الأعظمي لإشارة الدخل من أجل تحقيق شرط الإشارة الصغيرة.

السؤال الخامس:

ليكن لدينا المضخم التقاضي المبين بالشكل جانباً والمطلوب:

- 1- احسب احداثيات نقطة العمل للترانزستور في المضخم التالي إذا علمت أن:  $V_{CC} = 18V, V_{EE} = 18V, R_{EE} = 47 k\Omega, R_C = 100 k\Omega, \beta_F = 100$

- 2- احسب الربح في النمط التقاضي  $A_{dd}$  والربح في النمط المشترك  $A_{cc}$  واحسب نسبة رفض النمط المشترك CMRR بالنسبة للخرج المشترك وبالنسبة لخرج واحد.

- 3- احسب مقاومة الدخل  $R_{id}$  والخرج  $R_{od}$  للنمط التقاضي و مقاومة الدخل للنمط المشترك  $R_{ic}$ .

السؤال الأول (١٥ درجة):

٣ - (صح) ✓ ١ -

٤ - خطأ - الصحيح - في المنطقة الفعالة

أو - كفنا & الكتروني (switch)

٢ - خطأ ١ - الصحيح - ديوور واهد ٢

٤ - خطأ ١ - الصحيح - ملائمة التكافؤ

أو n-type

٥ - خطأ ١ - الصحيح - المرتفعة

السؤال الثاني (١٥ درجة):

٣ -  $E < 0.17$   $\Rightarrow$  الديود فتحار عكسي  $\Leftrightarrow$  يمثل مقاومة لازلية (دارة فكتور) أو تكون

$V_D = 0 \Leftrightarrow I_D = 0 \Leftrightarrow V_R = 0$   $\Rightarrow$  الدارة المكافئة بالشكل

السؤال الثالث (٢٠ درجة):

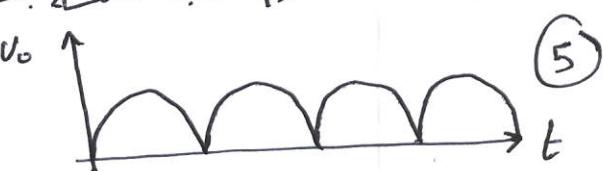

- عند مرور النسبة الموجية، يكون  $D_3$  و  $D_2$  فتحاريت أعادياً وبالتالي تمر السفحة الموجية فلماها

و فلاته المقاومة  $R$  عن الاتجاه الموجب للاتجاه

- عند مرور النسبة الالالية، يكون  $D_1$  و  $D_2$  فتحاريت أعادياً وبالتالي تمر النسبة الالالية فلماها

و فلاته المقاومة  $R$  عن الاتجاه الموجب. فتعتمد على تقويم ووجهة كاملة.

في هذه الديودات متالية:

$U_{DC} = 2(3.181V_m - 2V_0) = 6.361V_m = 6.361(101) = 63.62$  ٢

- وفي حال اعتبار الطابع الديودات غير متالية يكون

$$U_{DC} = 2(3.181V_m - 2V_0) = 6.361(101 - 20.17) = 54.696$$

السؤال الرابع ( 20 درجة ) :

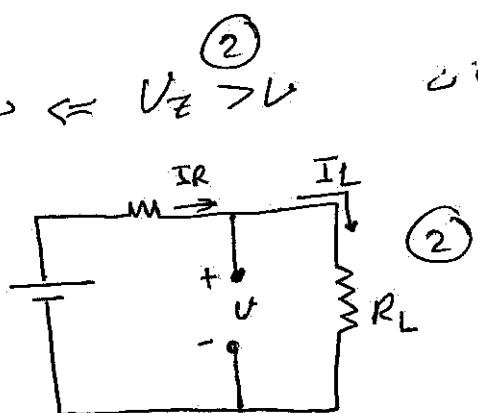

١- تزيله ديوود زينر وحسب معادله  $\leftarrow$

$$U = \frac{R_L}{R+R_L} U_i = \frac{1,2 \cdot 10^{+3} \cdot 16}{(1+1,2) \cdot 10^{+3}} = 8,73 \text{ V. } \quad (1)$$

$\Rightarrow$  ديوود زينر في حالة قطع  $\Rightarrow V_Z > U$  جاء

$$V_L = U = 8,73 \text{ V. } \quad (2)$$

$$\Rightarrow V_R = U_i - V_L \quad (2)$$

$$= 16 - 8,73 = 7,27 \text{ V.}$$

$$I_Z = 0 \quad (2), \quad P_Z = V_Z \cdot I_Z = 0 \text{ Watt} \quad (2)$$

Aton

**السؤال الأول (20 درجة):**

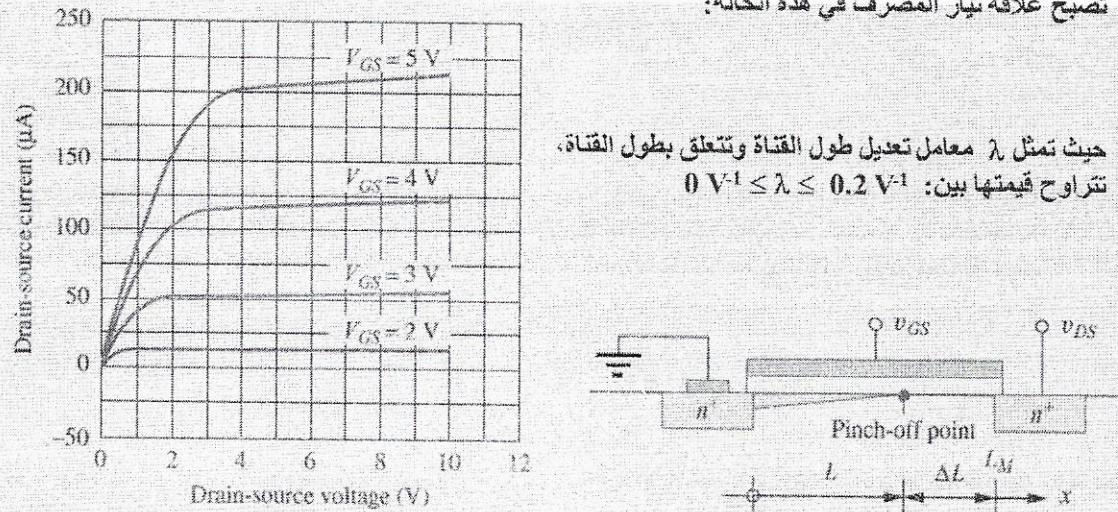

- (1)- وضع مع الرسم المبدأ الفيزيائي للترانزستور MOSFET - n-channel في النمط الافقاري، وارسم مميزة الترانزستور، ( $I_D$ ,  $V_{DS}$ )، ومميزة الترانزستور ( $I_D$ ,  $V_{GS}$ ). واكتب العلاقة الرياضية للتيار  $I_D$  في المنطقة الخطية وفي منطقة الاشباع

- (2)- وضع مع الرسم المبدأ الفيزيائي للترانزستور pnp - BJT عند تطبيق انحياز أمامي على الوصلة باعث - قاعدة وانحياز عكسي على الوصلة مجمع - قاعدة، واكتب العلاقة بين تيارات الترانزستور.

- (3)- اكتب علاقة التيار  $I_D$  بدلالة معامل تعديل طول القناة  $\lambda$  بالنسبة للترانزستور MOSFET وفسر فيزيائياً كيفية تعديل طول القناة مع رسم المميزة ( $I_D$ ,  $V_{DS}$ ).

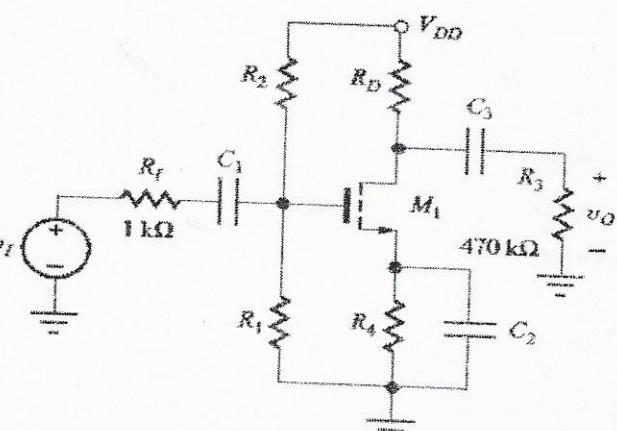

**السؤال الثاني (50 درجة): حل المسألتين الآتتين**

**المشألة الأولى (30):**

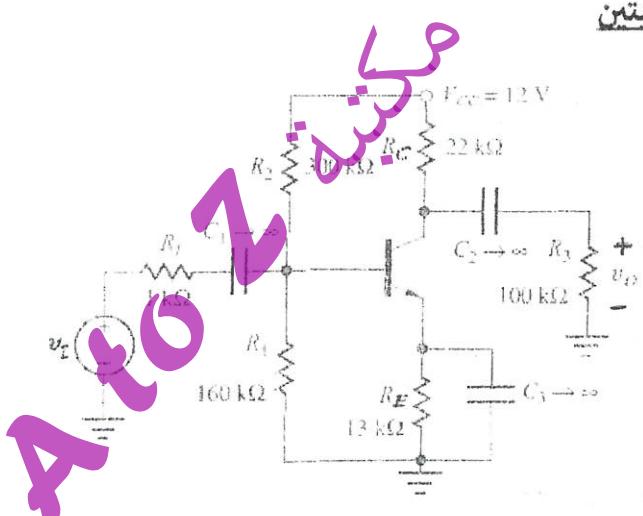

من أجل الدارة المبينة في الشكل، إذا علمت أن  $A_v = 50V$ ,  $V_A = 50V$ ,  $\beta = 65$ , والمطلوب:

- (أ)- جد إحداثيات نقطة العمل (حساب التحليل المستمر). (ب) رسم الدارة المكافئة للترانزستور من أجل تحليل الإشارة الصغيرة، واحسب معاملات الترانزستور.

(ج)- جد ربع الجهد

- (د)- حساب المطال الأعظمي لإشارة الدخل (استخدم علاقة شرط الإشارة الصغيرة للترانزستور BJT).

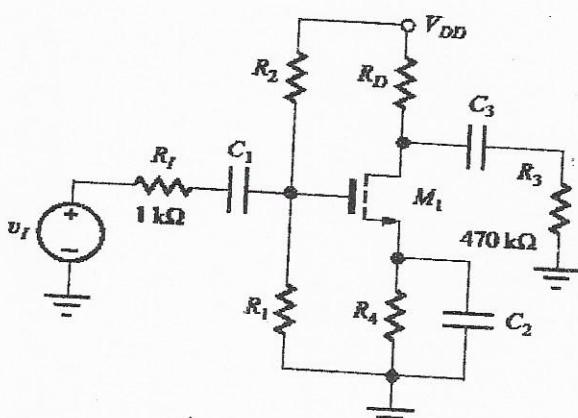

**المشألة الثانية (20):**

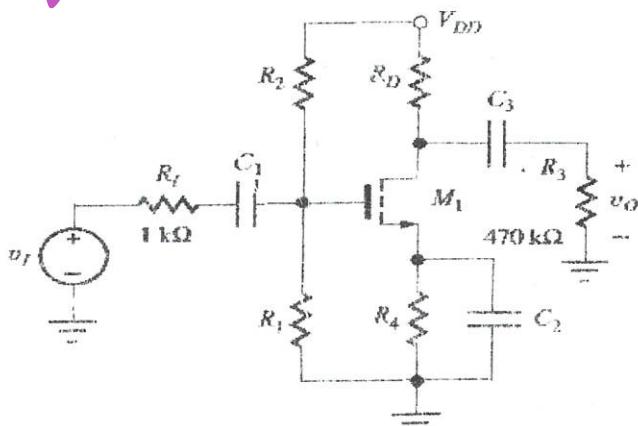

- (1)- ارسم الدارة المكافئة المستمرة للدارة المبينة في الشكل واحسب إحداثيات نقطة العمل Q-point، إذا علمت أن:

$$K_N = 250 \mu A/V^2 \quad V_{TN} = 1 V,$$

$$V_{DD} = 15 V, \quad R_1 = 1k\Omega, \quad R_2 = 2.7 M\Omega,$$

$$R_3 = 470 k\Omega, \quad R_4 = 27k\Omega,$$

$$V_{GSQ} = 1.8V$$

- (2)- من أجل نقطة العمل Q-point  $A_v = 82.2 \mu A, 6.04V$  جد ربع الجهد ومقاومة دخل الدارة ومقاومة خرج الدارة (على دخل وخرج الترانزستور مباشرة).

- (3)- حساب المطال الأعظمي لإشارة الدخل (استخدم علاقة شرط الإشارة الصغيرة للترانزستور MOSFET).

**السؤال الأول (24 درجة): (الوقت المتوقع الأعظمي للإجابة 40 دقيقة)**

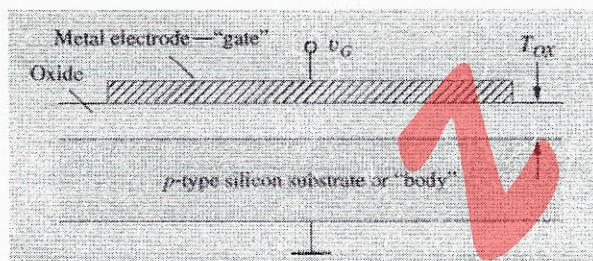

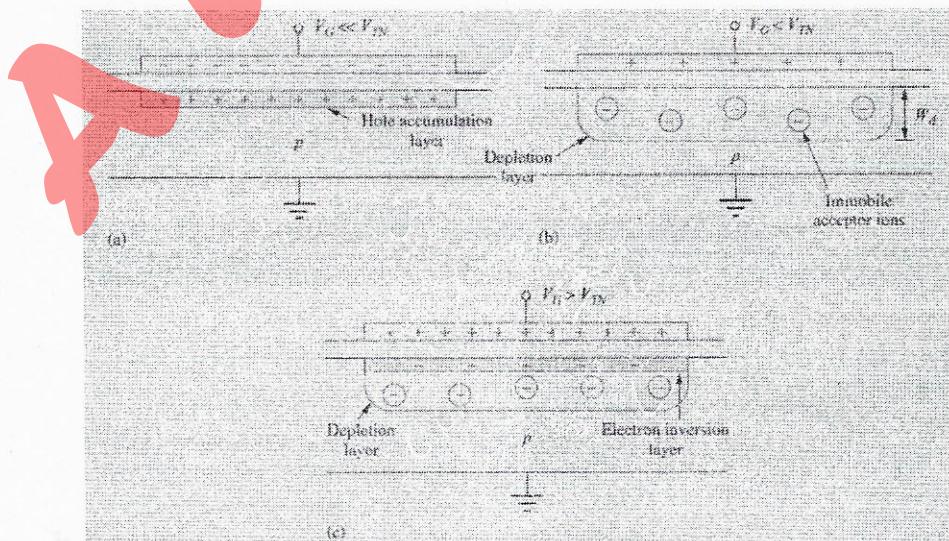

- (1)- وضح مع الرسم المبدأ الفيزيائي للمكثف MOS معرفاً من خلال هذا الشرح الجهد  $V_{TN}$  والطبقة المعاكسة، وارسم مميزة المكثف (علاقة سعة المكثف بالجهد المطبق على البوابة)، وارسم الدارة المكافئة للمكثف.

- (2)- ووضح مع الرسم المبدأ الفيزيائي للترانزستور MOSFET n-channel في النمط الإغاثي من أجل الجهد  $V_G$  وارسم مميزة المكثف (علاقة التيار  $I_D$  في المنطقة الخطية للتيار  $ID$  في المنطقة الرياضية للتيار  $ID$ )، وارسم الدارة المكافئة للمكثف.

- (3)- ووضح مع الرسم المبدأ الفيزيائي للترانزستور pnp - BJT عند تطبيق انحياز أمامي على الوصلة باعث - قاعدة وانحياز عكسي على الوصلة مجمع - قاعدة، واكتب العلاقة بين تيارات الترانزستور.

- (4)- اكتب علاقة التيار  $I_D$  بدلالة معامل تعديل طول القناة  $\lambda$  بالنسبة للترانزستور MOSFET وفسر فيزيائياً كيفية تعديل طول القناة مع رسم المميزة ( $I_D$ ,  $V_{DS}$ ).

**السؤال الثاني (46 درجة): حل المسألتين الآتتين (الوقت الأعظمي للإجابة 80 دقيقة)**

**المشألة الأولى (26):**

من أجل الدارة المبينة في الشكل، إذا علمت أن

$$V_A = 50V, \beta = 65, V_A = 50V$$

(أ)- جد إحداثيات نقطة العمل (حساب التحليل المستمر). (ب) رسم الدارة المكافئة للترانزستور من أجل تحليل الإشارة الصغيرة، واحسب معاملات الترانزستور.

(ج)- جد ربح الجهد  $A_V$  ومقاومة دخل الدارة ومقاومة خرج الدارة (يرجى الانتباه للأسهم)، حيث يتطلب حساب مقاومة الدخل ومقاومة الخروج. (د)- حساب المطال الأعظمي لإشارة الدخل (استخدم علاقه شرط الإشارة الصغيرة للترانزستور BJT).

**المشألة الثانية (20):**

(1)- ارسم الدارة المكافئة المستمرة للدارة المبينة في الشكل واحسب إحداثيات نقطة العمل Q-point، إذا علمت أن:

$$K_N = 250 \mu A/V^2, V_{TN} = 1V, V_{DD} = 15V, R_1 = 1k\Omega, R_2 = 2.7M\Omega, R_3 = 1M\Omega, R_4 = 470k\Omega, R_5 = 82k\Omega, R_6 = 27k\Omega, V_{GSQ} = 1.8V$$

(2)- من أجل نقطة العمل Q-point ( $82.2\mu A, 6.04V$ )، جد ربح الجهد  $A_V$  ومقاومة دخل الدارة ومقاومة خرج الدارة (على دخل وخرج الترانزستور مباشرة).

- (3)- حساب المطال الأعظمي لإشارة الدخل (استخدم علاقه شرط الإشارة الصغيرة للترانزستور MOSFET).

السؤال الأول (٢٤ درجة): (الوقت المتوقع الأعظمي للإجابة ٤٠ دقيقة)

(١) - وضح مع الرسم المبدأ الفيزيائي للمكثف MOS معروفاً من خلال هذا الشرح الجهد الجهد  $V_{TN}$  والطبيقة المعكوسة، وارسم مميزة المكثف (علاقة سعة المكثف بالجهد المطبق على البوابة)، وارسم الدارة المكافئة للمكثف.

يشكل فهم عمل مكثف MOS النواة الأساسية لفهم عمل الترانزستور الحقلي MOSFET.

يسخدم مكثف MOS لtransport شحن عند الحد الفاصل بين النصف ناقل والأوكسيد.

يشكل القطب الأعلى للمكثف من مادة ذات مقاومة منخفضة (معدن)، غالباً ما يكون الألمنيوم، أو مادة من بولي سيلكون مشابهة بشكل كثير، يُسمى هذا القطب بالبوابة Gate.

يفصل بين البوابة والمادة النصف ناقلة p-type (الجسم، أو الأسلاس) مادة عازلة رقيقة، سمكتها  $T_{OX}$  مشكّلة من أوكسيد السيلكون (Oxide). يُعد أوكسيد السيلكون مادة مستقرة وثابتة، عازل ممتاز، هذا يفسر أحد الأسباب لانتشار السيلكون كمادة نصف ناقلة. تعمل المادة p-type عمل القطب الثاني للمكثف. يمكن تصنيع المكثف من مادة نصف ناقلة نوع n. تعمل التشكيلة المبينة عمل مكثف متغير لآخر، يتم التحكم بقيمتها من خلال الجهد المطبق.

في حال تطبيق جهد شيد السلبية على البوابة G ( $V_G < V_{TN}$ ) بالنسبة للأسلاس substrate (الشكل (a)). حيث  $V_{TN}$  عبارة عن جهد عتبة. يتم تعديل سلبية الجهد المطبق من خلال التقوّب الموجود في المادة نوع p (الكريمية) التي تتجمع (عملية تحانب) حول طبقة الأوكسيد، مشكّلة طبقة شمي الطبة المجمعة accumulation.

تبدأ سلبية جهد البوابة بالانخفاض التدريجي حتى تصبح قطبية جهد البوابة موجبة ( $V_G > V_{TN}$ ) (الشكل (b)) ، تبدأ التقوّب بالابتعاد عن الحد الفاصل للأوكسيد بسبب التناقض بين قطبيتين موجبتيين. تختلف التقوّب وراءها شوارد الأخذ acceptor السالبة، وبالتالي تتشكل منطقة من الشوارد (خالية من حوامل الشحنة)، تُسمى هذه المنطقة بالمنطقة المجردة depletion region. تتعادل قطبية الجهد المطبق الموجب مع الشوارد السالبة على الطرف الأسفل للأوكسيد. يُعطى عرض المنطقة المجردة بالرمز  $w_d$  حوالي بضعة ميكرو متر حسب قيمة الجهد المطبق.

بزيادة الجهد المطبق على البوابة حيث يصبح ( $V_G > V_{TN}$ ) (الشكل (c)), تنجذب الإلكترونات من الحد الفاصل للأوكسيد وتتجاوز كثافة الإلكترونات كثافة التقوّب، عند هذه القيمة للجهد  $V_{TN}$  تقلب قطبية المادة من النوع p إلى مادة من نوع n على الحد الفاصل للأوكسيد. تُسمى المنطقة الجديدة نوع n بالمنطقة (أو الطبة) المقلوبة أو المعكوسة inversion region (or inversion layer). تتعادل قطبية الجهد المطبق الموجبة مع كثافة الإلكترونات الموجودة على الحد الفاصل للأوكسيد مباشرة بالإضافة للشوارد السالبة الموجودة ضمن المنطقة المجردة. تُسمى قيمة الجهد التي تقلب عنده نوعية المادة من النوع p إلى النوع n بجهد العتبة threshold voltage  $V_{TN}$ .

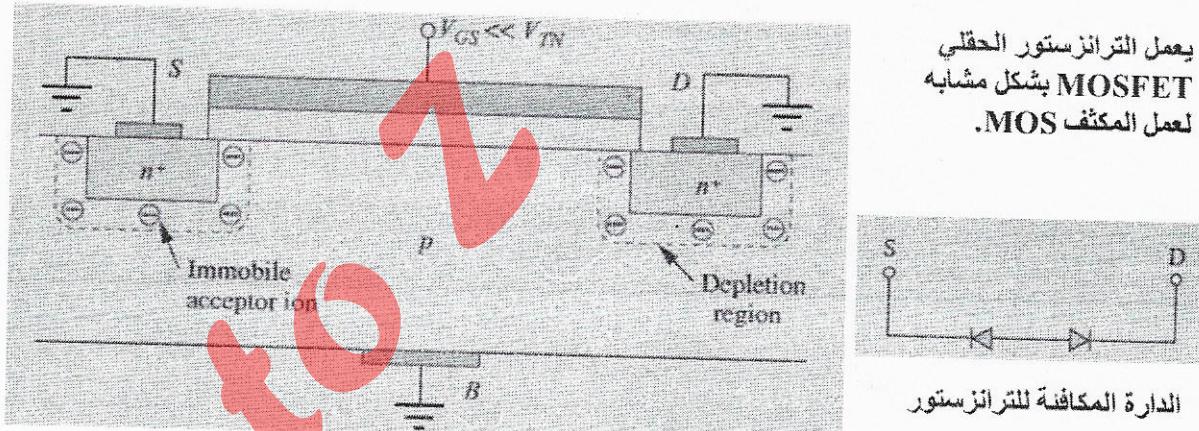

(٢)- وضح مع الرسم المبدأ الفيزيائي للترازستور MOSFET n-channel في النمط الإغاثي من أجل الجهد  $V_G$  ، وكتب العلاقة الرياضية للتيار  $I_D$  في المنطقة الخطية مع شروط قيم الجهد، وكتب العلاقة الرياضية للتيار  $I_D$  في منطقة الاشباع مع تحديد شروط قيم الجهد، ورسم ممizza الترازستور  $V_{DS}$  مواضعاً مناطق عمل الترازستور.

(١)- عند تطبيق جهد شديد السلبية على البوابة G بالنسبة للأساس  $V_G << V_{TN}$  . حيث عبارة عن جهد عتبة وعنه تقلب القناة من نوع p إلى النوع n (من تسمية الترازستور NMOS أي نوع القناة n-type) . الدارة المكافحة للترازستور عبارة عن وصلة متصل شانياً back-to-back، وبالتالي يمر صغير جداً بين المنبع والمصرف وهو عبارة عن تيار عكسى  $I_D = I_{DSS}$

لاحظ أن الأساس substrate والمنبع والمصرف كلها موصولة إلى الأرض.

(٢)- عند تطبيق ( $V_G > V_{TN}$ ). تبدأ الثقوب بالابتعاد عن الحد الفاصل للأوكسيد بسبب التناحر بين قطبيتين موجبتين. تخلف الثقوب وراءها شوارد الآخذ acceptor السالبة، وبالتالي تتشكل منطقة من الشوارد (خلية من حوامل الشحنة)، تسمى هذه المنطقة بالمنطقة المجردة depletion region. لا تضم حوامل شحنة، وبالتالي يوجد تيار بين المنبع والمصرف.

(٣)- عند تطبيق ( $V_G > V_{TN}$ ). تتجذب الإلكترونات من الحد الفاصل للأوكسيد وتنتجاوز كثافة الإلكترونات كثافة الثقوب، عند هذه القيمة للجهد  $V_G > V_{TN}$  على الحد الفاصل للأوكسيد. تسمى مادة من نوع n على الحد الفاصل للأوكسيد inversion layer (أو الطبقة) الجديدة نوع n بالمنطقة inversion layer (or المحفوظة المقلوبة). وبالتالي يتدفق تيار بين المنبع والمصرف.

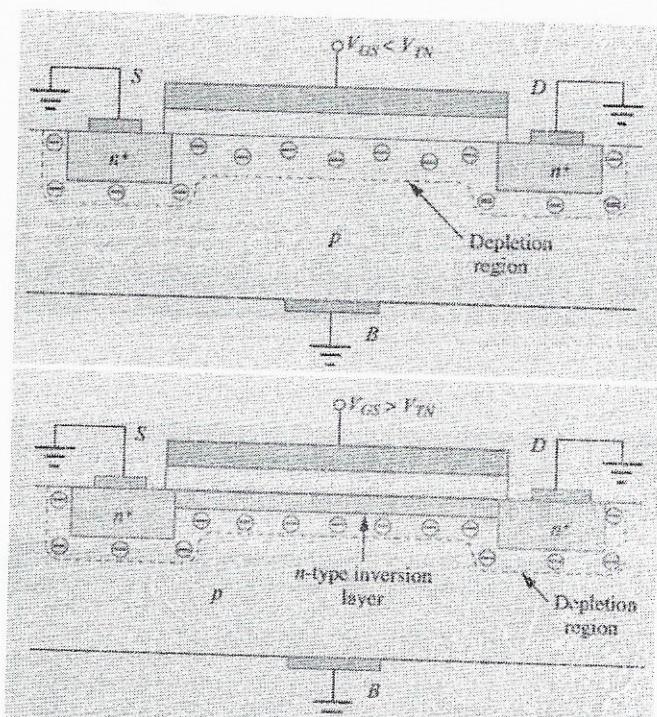

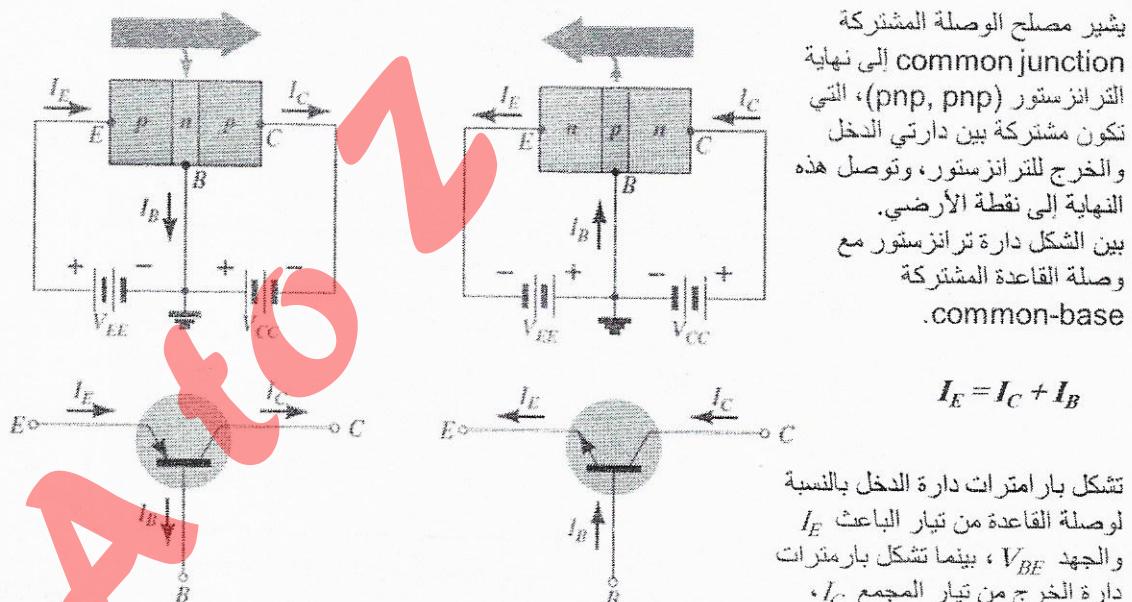

(٣)- وضح مع الرسم المبدأ الفيزيائي للترانزستور pnp - BJT عند تطبيق انحياز أمامي على الوصلة باعث - قاعدة وانحياز عكسي على الوصلة مجمع - قاعدة، واكتب العلاقة بين تيارات الترانزستور.

Notation and symbols used with the common-base configuration:

(a) pnp transistor; (b) npn transistor.

(٤)- اكتب علاقة التيار  $I_D$  بدلالة معامل تعديل طول القناة  $\lambda$  بالنسبة للترانزستور MOSFET وفسر فيزيائياً كيفية تعديل طول القناة مع رسم المميزة ( $I_D$ ,  $V_{DS}$ ).

تبين المميزة العملية للترانزستور NMOS أن تيار المصرف  $I_D$  ليس ثابتاً تماماً، بل هناك ميل صغير في المميزة، بمعنى أن تيار المصرف يزداد بشكل طفيف جداً ضمن منطقة الأشباع. تنشأ هذه الزيادة في تيار المصرف نتيجة لظاهرة تُدعى تعديل طول القناة channel-length modulation. تنشأ هذه الظاهرة كون الطول الفعلي للقناة  $L = L_M - \Delta L$  ، ينقص مع زيادة  $\Delta L$  التي تنتج عن زيادة الجهد  $V_{DS} > V_{DS(\text{sat})}$ . تصبح علاقة تيار المصرف في هذه الحالة:

السؤال الثاني (٦٤ درجة): حل المسألتين الآتتين (الوقت الأعظمي للإجابة ٨٠ دقيقة)

المشارة الأولى (٢٦):

- من أجل الدارة المبينة في الشكل، إذا علمت أن  $V_A = 50V$ ,  $\beta = 65$ , والمطلوب:

- جد أحاديث نقطة العمل (حساب التحليل المستمر). (ب) رسم الدارة المكافئة للترانزستور من أجل تحليل الإشارة الصغيرة، واحسب معاملات الترانزستور.

- جد ربع الجهد  $Av$  ومقاومة دخل الدارة ومقاومة خرج الدارة (يرجى الانتباه للأسهم، حيث يطلب حساب مقاومة الدخل ومقاومة الخروج). (د) حساب المطال الأعظمي لإشارة الدخل (استخدم علامة شرط الإشارة الصغيرة للترانزستور BJT).

Writing an equation for the output loop containing  $V_{CE}$ :

$$5 - 10^4 I_C - V_{CE} - 1.6 \times 10^4 I_E - (-5) = 0$$

$$V_{CE} = 10 - 10^4 I_C - 1.6 \times 10^4 I_E = 10 - 2.41 - 3.92 = 3.67 \text{ V}$$

$$(I_C, V_{CE}) = (0.241 \text{ mA}, 3.67 \text{ V})$$

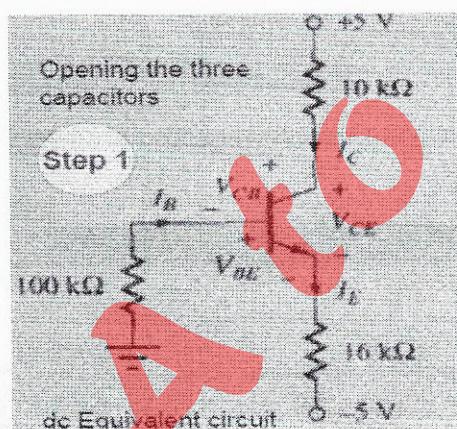

Q-Point Analysis:

The first step is to draw the dc equivalent circuit to compute the Q-point.

$$I_E = (\beta_F + 1) I_B$$

$$10^5 I_B + V_{BE} + (\beta_F + 1) I_B (1.6 \times 10^4) = 5$$

$$10^5 I_B + 0.7 + 66 I_B (1.6 \times 10^4) = 5$$

$$I_B = \frac{(5 - 0.7) \text{ V}}{10^5 \Omega + 1.06 \times 10^6 \Omega} = 3.71 \mu\text{A}$$

$$I_C = 65 I_B = 241 \mu\text{A}$$

$$I_E = 66 I_B = 245 \mu\text{A}$$

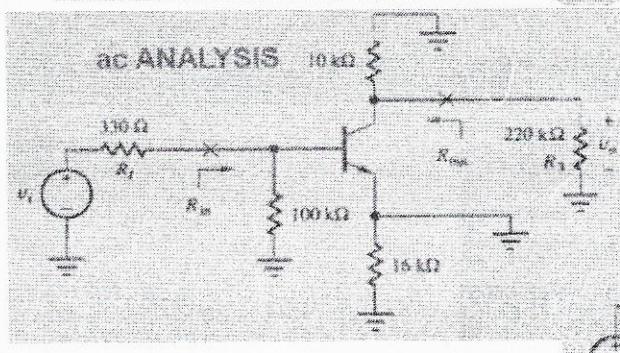

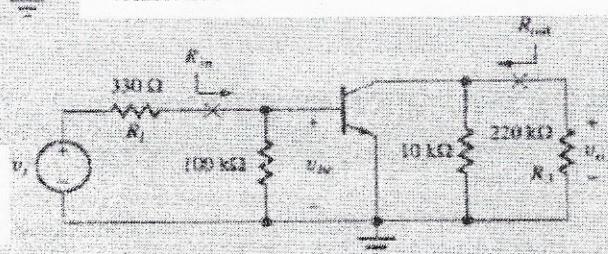

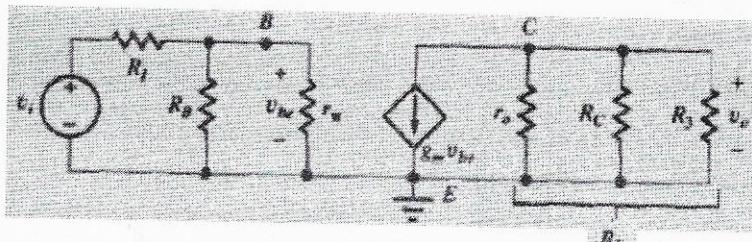

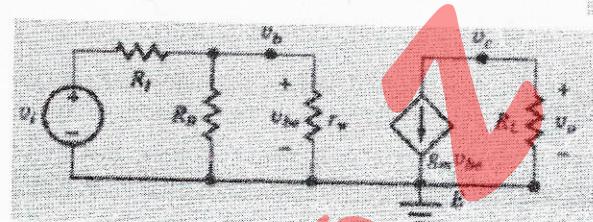

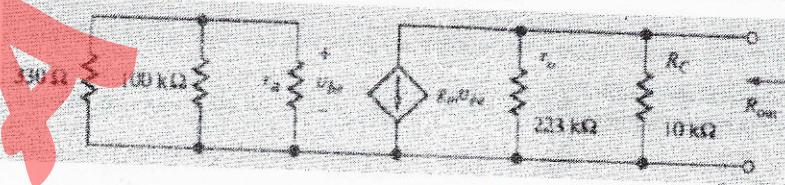

Step 2

The next step is to draw the ac equivalent circuit and simplify it before beginning the detailed analysis. For the ac analysis, we replace all capacitors by short circuits and the dc voltage sources with ground connections.

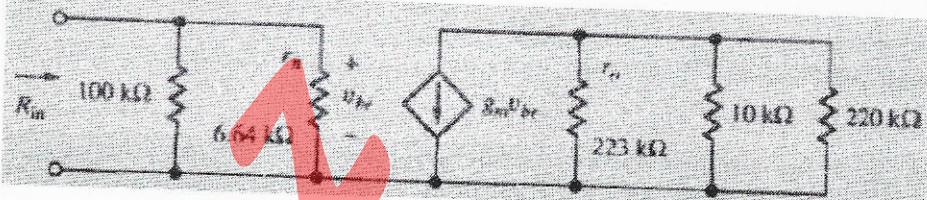

$$g_m = 40 I_C = \frac{40}{V} (2.41 \times 10^{-4} \text{ A}) = 9.64 \times 10^{-3} \text{ S}$$

$$r_o = \frac{\beta_F V_T}{I_C} = \frac{65(0.025 \text{ V})}{2.41 \times 10^{-4} \text{ A}} = 6.64 \text{ k}\Omega \quad \text{Step 4}$$

$$r_d = \frac{V_A + V_{CE}}{I_C} = \frac{(50 + 3.67) \text{ V}}{2.41 \times 10^{-4} \text{ A}} = 223 \text{ k}\Omega \quad \mu_f = g_m r_o = (58.0 \text{ mS})(54.1 \text{ k}\Omega) = 3140.$$

Common-emitter amplifier

Step 3

Voltage gain  $A_v$

Step 5

The output voltage  $v_o$  is equal to the negative of the controlled-source current times the value of the load resistor

$$v_o = -(g_m v_{be}) R_L$$

which gives  $A_{vt} = -g_m R_L$

$$A_{vt} = \frac{v_c}{v_b} = \frac{v_o}{v_{be}}$$

Voltage gain  $A_v$

Now we are ready to develop an expression for the overall voltage gain of the amplifier. First, we find the terminal voltage gain  $A_{vt}$  between the base and collector terminals of the transistor. We then use this expression to find the gain of the overall amplifier. Starting with the circuit the terminal voltage gain is defined as

P

Now let us find the overall gain of the amplifier from source  $v_i$  to the output voltage across  $R_3$ . The gain can be written as

$$A_v = \frac{v_o}{v_i} = \left( \frac{v_o}{v_{be}} \right) \left( \frac{v_{be}}{v_i} \right) = A_{vt} \left( \frac{v_{be}}{v_i} \right)$$

Voltage divider

$$v_{be} = \frac{R_B \| r_\pi}{R_I + (R_B \| r_\pi)} v_i \quad \rightarrow \quad A_v = -g_m R_L \left[ \frac{R_B \| r_\pi}{R_I + (R_B \| r_\pi)} \right]$$

$$A_v = -(9.64 \times 10^{-3})(9.57 \text{ k}\Omega \| 220 \text{ k}\Omega) \left( \frac{6.23 \text{ k}\Omega}{330 \Omega + 6.23 \text{ k}\Omega} \right) = -84.0$$

$A_v$  in decibel is equal to  $A_v / \text{dB} = 10 \log(V_o/V_i)$

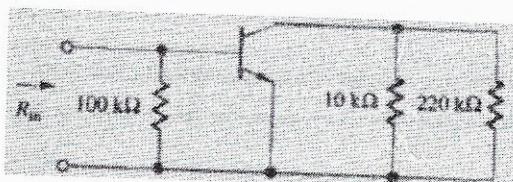

The input resistance is defined looking into the amplifier at the position of coupling capacitor C1

$$R_{in} = 100 \text{ k}\Omega \| r_{be} = 100 \text{ k}\Omega \| 6.64 \text{ k}\Omega = 6.23 \text{ k}\Omega$$

Step 5

The output resistance is defined looking back into the amplifier at the location of coupling capacitor C3

$$R_{out} = r_o \| R_C = 223 \text{ k}\Omega \| 10 \text{ k}\Omega = 9.57 \text{ k}\Omega$$

Step 5

Small-signal operation requires  $|v_{be}| \leq 0.005 \text{ V}$ .

$$v_{be} = \frac{R_B \| r_x}{R_{in} + (R_B \| r_x)} v_i$$

Step 6

$v_{in} = 0.00475 \text{ V}$

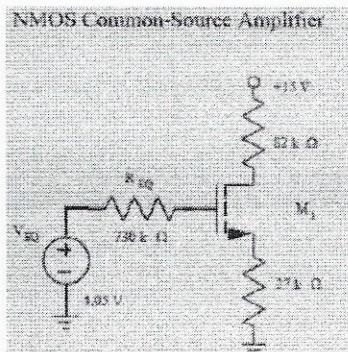

### المشألة الثانية (٢٠) :

(١)- ارسم الدارة المكافئة المستمرة للدارة المبينة في الشكل واحسب إحداثيات نقطة العمل Q- point، إذا علمت أن:

$$\begin{aligned} K_N &= 250 \mu\text{A}/\text{V}^2 \quad V_{TN} = 1 \text{ V}, \\ V_{DD} &= 15 \text{ V}, \quad R_1 = 1 \text{k}\Omega, \quad R_1 = 1 \text{ M}\Omega, \\ R_2 &= 2.7 \text{ M}\Omega, \quad R_D = 82 \text{ k}\Omega, \quad R_4 = 27 \text{k}\Omega, \\ V_{GSQ} &= 1.8 \text{ V} \end{aligned}$$

(٢)- من أجل نقطة العمل Q-point، جد ربح الجهد  $A_V$  و مقاومة دخل الدارة و مقاومة خرج الدارة (على دخل و خرج الترانزستور مباشرة).

- (٣)- حساب المطال الأعظمي لإشارة الدخل (استخدم علاقة شرط الإشارة الصغيرة للترانزستور (MOSFET)).

$$V_{EQ} = 15V \frac{1M\Omega}{1M\Omega + 2.7M\Omega} = 4.05V$$

$$R_{EQ} = 1M\Omega \parallel 2.7M\Omega = 730k\Omega$$

$$I_D = \frac{0.25mA}{2} (V_{GS} - 1)^2 \quad I_D = 82.2 \mu A$$

$$V_{DS} = 15 - 82000I_D - 27000I_D = 6.04V$$

Q-point: (82.2 μA, 6.04 V)

What is the voltage gain of the amplifier in Fig. P13.106? Assume  $K_n = 0.500 \text{ mA/V}^2$ ,  $V_{TN} = 1 \text{ V}$ , and  $\lambda = 0.0133 \text{ V}^{-1}$ .

For the bias network:  $V_{EQ} = 10V \frac{430k\Omega}{430k\Omega + 560k\Omega} = 4.343V \quad | \quad R_{EQ} = 430k\Omega \parallel 560k\Omega = 243k\Omega$

$$I_D = \frac{5 \times 10^{-4}}{2} (V_{GS} - 1)^2 \quad | \quad V_{GS} = 4.343 - 2 \times 10^4 I_D \rightarrow V_{GS} = 1.72 \text{ V} \quad | \quad I_D = 131 \mu A$$

$V_{DS} = 10 - 63k\Omega(131\mu A) = 1.75V \geq V_{GS} - V_{TN}$  so active region assumption is ok.

$$g_m = \sqrt{2(5 \times 10^{-4})(131\mu A)} = 362 \mu S \quad | \quad r_o = \left( \frac{1}{0.0133} + 1.75 \right) = 586k\Omega$$

$$A_v = -\frac{243k\Omega}{243k\Omega + 1k\Omega} (362 \mu S)(586k\Omega \parallel 43k\Omega \parallel 100k\Omega) = -10.3$$